石英晶體振盪器和周邊電路設計指南 (中)

雜訊消除與抑制對策

序前篇技術文件「雜訊抑制電路設計方法」,我們了解到相關雜訊的來源(石英晶體振盪器內部IC以及其周邊電路/電源端與輸出訊號端)。

在本篇章節,我們將會進一步探討與說明,如何降低與抑制雜訊的解決方式。

首先,主要降低雜訊的方式,有以下三種設計參考:

1. 建立穩定的電源與接地設計

2. 抑制電源雜訊的濾波線路設計 (安裝濾波線路以防止由電源所發出的雜訊)

3. 穩定的輸出訊號線配置

在此章節將會先以下列兩項參考設計解決方式進行說明;

1. 建立穩定的電源與接地設計

2. 抑制電源雜訊的濾波線路設計

1. 穩定的電源和接地設計

穩定的電源和接地設計,是基於在高頻的頻段會有較低的阻抗,同時為了實現在各頻寬下各頻率點都能有均勻電位的導通特性考量。而接地線代表電路的基本參考電位,透過更寬闊表面積的接地層設計,以提供最穩定的設計特性。

當在採用多層板設計時,可透過額外的接地層來配置獨立的電源線和接地線。

關於焊點設計的部份,採用更寬的接觸面積可確保較低的阻抗,進而降低雜訊產生。

2. 電源線濾波設計

透過搭配石英晶體振盪器的電路設計為例,通常會在電源端和接地線之間設計一個濾波線路,除了可防止由石英晶體振盪器的雜訊洩漏到電源端或接地線,同時也可避免由電源線向石英晶體振器發出雜訊干擾。

而最為常用的濾波線路設計,大多會是在電源線和接地線之間連接一個或多個旁通電路專用濾波電容器。

a .旁通電路專用濾波電容器

旁通電路上的濾波電容的工作原理,主要是用來降低電阻(抗)間的相互作用,目的在於可以幫助提高整體電路的穩定運作,同時可吸收存在於電源線上的雜訊,這是最為普遍用來降低雜訊的方法。而透過適當的電容器容值設計選用,可以解決大多數與雜訊相關的問題。

i.旁通電路電容器容量選用

標準旁通電路電容值,如果只設計一顆時,建議約保持在0.01μF至1μF間,此旁通電路電容值建議盡可能越小越好。

同時,必須確認此旁通電路電容器電容值的頻率特性,以確保在高頻或低頻段時的阻抗不會增加。

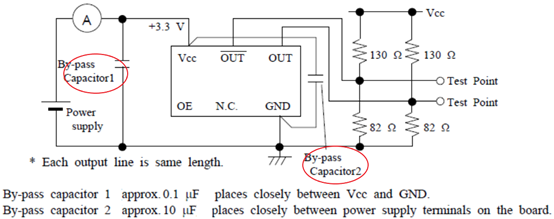

下圖參考(高耗電,對電源雜訊極度敏感的「差動式輸出」石英晶體振盪器電路設計),當旁通電路濾波用電容採用兩顆設計,電容器一容值約0.1μF,建議置放於愈接近Vcc和GND走線間。

電容器二容值約10μF,建議置放於愈接近電路板上電源走線路徑上。

採用兩顆旁通電路電容器大、小電容量時,可以分別過濾來自電源線上的高頻、低頻雜訊。

i i.旁通電路電容實裝設計

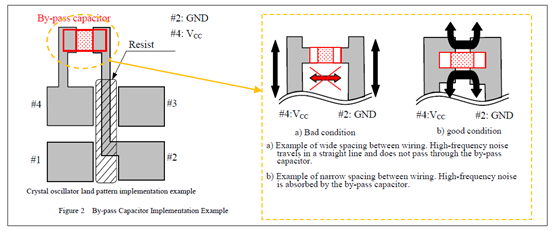

為了降低雜訊干擾,旁通電路用電容應盡可能靠近石英晶體振盪器。因為隨著走線長度的增加,寄生電感特性也將隨之增加,並導致高頻阻抗特性增大,所以必須留意旁通電路電容器的走線設計,以便讓信號可經由旁通電路電容器再流通過電源線,這可強制讓雜訊通過旁通電路電容器,有效提高雜訊消除。

然而,高頻雜訊通常會以直線方式來傳遞,所以在設計旁通電路電容時,請務必避免使用圖2a中的設計方式。如果是使用圖2a的設計方式,雜訊將不會通過旁路電容器而無法達到抑制的效果。因此,我們建議採用圖2b中顯示的圖面設計。

本篇為「石英晶體振盪器周邊電路的設計參考原則 (中)」,我們將於下期介紹,如何透過優化電路走線方法和設計,降低來自電路雜訊的設計建議,敬請期待。